Schwachstellen

17.01.2018, 15:55 Uhr

Meltdown und Spectre: Lesen ohne zu lesen

Was Meltdown und Spectre mit einem Schachspiel zu tun haben und worum es bei den Sicherheitslücken aus technischer Sicht geht. Ein Informatikprofessor erklärt.

Von Marcel Waldvogel

Die Sicherheitslücken Meltdown und Spectre sind zurzeit in aller Munde und werden uns noch lange beschäftigen. Denn die Schwachstellen sind tief verwurzelt in der Art, wie man Prozessoren heute schnell macht. Sie erlauben es, Daten zu lesen, ohne dass ein Kommando zum Lesen dieser Daten ausgeführt werden muss, mit der Folge, dass die üblichen Überprüfungen, ob dieser Lesebefehl auch berechtigt ist, ins Nichts laufen: ein riesiges Sicherheitsproblem! Deshalb sollten nicht nur eingefleischte Informatiker die Hintergründe verstehen.

Mein Versuch einer Erklärung für alle beginnt mit einem Schachspiel zwischen blutigen Anfängern; und endet mit einem Ausblick, was auf die IT-Industrie und uns alle zukommt.

1. Hintergrund und Überblick

Schach...

Zwei Anfänger, Melt Down und Pro Zessor, spielen gegeneinander Schach. Pro Zessor weiss nicht weiter. Melt Down, verzweifelt ab dem langen Warten, verabschiedet sich für 10 Minuten, um gegenüber einen Döner essen zu gehen. Pro Zessor beginnt, da sein Vorstellungsvermögen nicht so toll ist, auf dem Schachbrett mögliche nächste Züge auszuprobieren. Rechtzeitig vor der Rückkehr seines Gegners stellt er aber alle Figuren wieder an den ursprünglichen Platz und wähnt sich sicher.

Melt Down ist aber ausgefuchster, als er aussieht. Nach seiner Rückkehr schaut er flach über das Schachbrett und sieht, auf welchen Feldern weniger Staub liegt und kann damit die Strategie des armen Pro Zessor einmal mehr durchkreuzen [1].

… und Prozessoren

So ähnlich funktionieren auch die Meltdown- und Spectre-Angriffe gegen Prozessoren: Der Prozessor schaut immer etwas voraus, damit er so schnell ist, wie wir ihn uns wünschen. Allerdings hinterlässt dieses Vorausschauen (die Informatiker nennen das «spekulative Ausführung» bzw. ennet dem Teich «speculative execution») Spuren, ähnlich unauffällig und kurzfristig wie Staub. Aber wenn ein Gegner weiss, worauf er schauen muss, kann er auch schwächste Spuren deuten. Darüber hinaus ist es recht einfach möglich, den Prozessor dazu zu bringen, auf einem möglichst staubigen Schachbrett zu spielen und so noch mehr Spuren zu hinterlassen.

Aber wieso sind Prozessoren so naiv? Zuerst einmal sind sie darauf trainiert, alles zu machen, was ihnen der Programmierer befiehlt, solange es nicht explizit verboten ist. Zum anderen sind Prozessoren heute nur so leistungsfähig, weil sie hinter dem Rücken des Programmierers versuchen, Abkürzungen zu nehmen, die dann hoffentlich nicht auffallen.

Abkürzungen …

Wieso ist das alles nötig? Und wieso sind wir in dieses Schlamassel reingerutscht? Schauen wir etwas zurück.

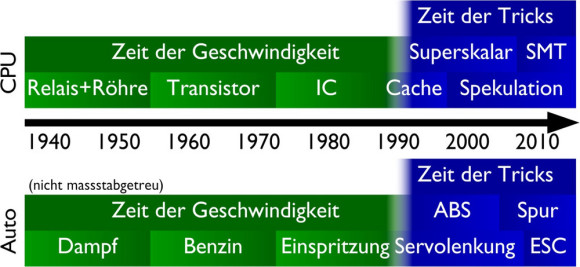

Die ersten programmierbaren Computer entstanden in den 1940er-Jahren und bestanden aus Tausenden von Relais. Das Schalten ging langsam (Hunderstelsekunden), die Leitungen waren (nicht nur sprichwörtlich) lang. Mit der Zeit wurden die Schaltvorgänge durch Röhren und Transistoren immer schneller und die Übertragungswege durch kleinere Bauteile, weniger Abwärme und später integrierte Schaltungen immer kürzer.

Die ersten programmierbaren Computer entstanden in den 1940er-Jahren und bestanden aus Tausenden von Relais. Das Schalten ging langsam (Hunderstelsekunden), die Leitungen waren (nicht nur sprichwörtlich) lang. Mit der Zeit wurden die Schaltvorgänge durch Röhren und Transistoren immer schneller und die Übertragungswege durch kleinere Bauteile, weniger Abwärme und später integrierte Schaltungen immer kürzer.

Zeitachse der Prozessor- und Autoentwicklung: früher echte Geschwindigkeit, heute eher (Komfort-)Trickserei

Quelle: Marcel Waldvogel, marcel-waldvogel.ch

Doch wirklich schneller wurden die Schaltgeschwindigkeiten nachher nicht mehr. Und es kam dazu, dass der Hauptspeicher, das RAM, das ausserhalb des Prozessors liegt, zwar immer noch grösser, aber kaum mehr schneller wurde.

… und Tricks

Den Bedarf an schnelleren Prozessoren konnte man also kaum mehr einfach durch Verkleinerung der Komponenten lösen [2]. Also mussten Tricks her, damit es weiterhin so aussah, als ob schön brav ein Befehl nach dem anderen ausgeführt werde, aber intern mehrere Befehle gleichzeitig abgearbeitet werden konnten. Das machte den Chip zwar komplizierter, aber Platz genug war ja da, da die Verkleinerung weiterhin voranschritt. Diese wichtigsten Tricks sind der Cache und die oben schon erwähnte spekulative Ausführung.

Auto = CPU?

Prozessoren stehen da nicht ganz alleine da. In vielen anderen technischen Geräten lief eine ähnliche Entwicklung ab: Über Jahrzehnte hinweg konnten sie schneller und kräftiger gemacht werden. Irgendwann ging aber nur noch kleiner, was aber häufig nicht mehr alle Bedürfnisse abdeckt. So auch bei den Autos: Da konnte vor Jahrzehnten noch viel aus dem Motor herausgekitzelt werden und Höchstgeschwindigkeit war ein wichtiges Unterscheidungsmerkmal. Heute ist aus Sicht des Käufers am Motor kaum mehr etwas zu verbessern, also mussten andere Argumente her, wie z.B. schnellere Reaktionen oder kürzere Bremswege und die ganzen Assistenten, die es weiterhin erlauben, Zeit zu sparen, aber nicht mehr durch reale Erhöhung der Geschwindigkeit.

Über den Autor und den Beitrag

Der Originaltext stammt vom Weblog von Marcel Waldvogel, der uns freundlicherweise erlaubt hat, den Text zu verwenden.

Marcel Waldvogel ist Spezialist für IT-Sicherheit und Informatikprofessor an der Universität Konstanz. Er bedankt sich bei Patrick Stählin («Schach»), Matthias Fratz und Gaby Salvisberg für Ideen, Diskussionen und Korrekturen.

Wie funktionieren die Tricks?

Caching

Der eine Trick ist so weitverbreitet und bekannt, dass ihn wohl keiner mehr als Trick ansieht, obwohl er es ist: Caching. Der Trick besteht darin, so zu tun, als ob der Hauptspeicher schneller sei, als er wirklich ist. Deshalb werden Daten, die der Prozessor aus dem grossen Hauptspeicher lädt, zusätzlich im Prozessor noch in einem kleinen Zwischenspeicher (Cache) aufbewahrt. Die Erfahrung zeigt nämlich, dass viele Speicherinhalte mehrfach verwendet werden. Ab der zweiten Verwendung müssen sie aber nicht mehr aus dem langsamen Hauptspeicher geladen werden, sondern kommen aus dem viel schnelleren Cache: Es wird ein viel schnellerer Hauptspeicher vorgegaukelt. Dieser Zeitunterschied ist für ein Programm messbar und eine wichtige Komponente des Angriffs.

Pipelining

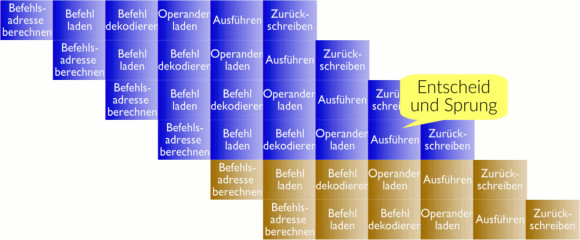

Seit rund 75 Jahren funktionieren die Prozessoren nach folgendem einfachem Prinzip: Es werden der Reihe nach Befehle aus dem Hauptspeicher geladen und ausgeführt (grüner Ablauf). Seit gut 25 Jahren werden Befehle aber überlappend ausgeführt: Der nächste Befehl wird schon in Angriff genommen, bevor der vorherige fertig ist (blauer Ablauf, genannt Pipelining; je nach Prozessor und ausgeführtem Befehl kann die Anzahl Pipelinestufen variieren). Dem Programmierer wird aber nach wie vor vorgegaukelt, der Prozessor arbeite nach dem grünen Prinzip.

Pipelining ist vergleichbar mit der Herstellung von Autos am Fliessband: Der Zusammenbau eines einzelnen Autos dauert weiterhin mehrere Tage; trotzdem verlässt alle paar Minuten ein neues Auto die Produktionsstrasse. Ein riesiger Produktivitätsgewinn.

Dieses einfache Pipelining im Prozessor läuft gut, solange der Prozessor keine Entscheidungen treffen muss. Entscheidungen im Prozessor sind sehr häufig: Was macht der Benutzer gerade? Ist die Festplatte endlich bereit? Wo hat es noch Platz im Hauptspeicher? Ist die Eingabe gültig? Je nachdem, wie diese Entscheidung ausgeht, werden andere Befehle ab einer anderen Speicheradresse geladen und ausgeführt. Diese Änderung der Adresse, ab welcher der nächste Befehl ausgeführt wird, heisst «Sprung».

Pipelining im Prozessor unterscheidet sich aber in einer Beziehung grundlegend vom Montageband: Ein Produktionsschritt bei einem Auto kann bestimmen, dass alle nachfolgenden Autos ganz anders zusammengebaut werden sollen.

Zum Zeitpunkt der Ausführung des Sprungbefehls sind aber schon viele andere Befehle (braun in der Grafik rechts) in der Pipeline. Solange nicht klar ist, ob sie ausgeführt werden sollen oder nicht, kann bei einer einfachen Pipeline gar nichts passieren: Der riesige Geschwindigkeitsvorteil durch die Pipeline ist bei jedem Sprungbefehl dahin.

Pipelining im Prozessor unterscheidet sich aber in einer Beziehung grundlegend vom Montageband: Ein Produktionsschritt bei einem Auto kann bestimmen, dass alle nachfolgenden Autos ganz anders zusammengebaut werden sollen.

Zum Zeitpunkt der Ausführung des Sprungbefehls sind aber schon viele andere Befehle (braun in der Grafik rechts) in der Pipeline. Solange nicht klar ist, ob sie ausgeführt werden sollen oder nicht, kann bei einer einfachen Pipeline gar nichts passieren: Der riesige Geschwindigkeitsvorteil durch die Pipeline ist bei jedem Sprungbefehl dahin.

Spekulative Ausführung

Seit bald 25 Jahren wird deshalb bei einem Sprungbefehl die Pipeline nicht leer gelassen, sondern der Prozessor versucht vorherzusagen, ob ein Sprung genommen werden soll oder nicht. Wenn die Vorhersage sich als richtig herausstellt, ist unser Prozessor viel schneller als alleine mit Pipelining. Im anderen Fall müssen die Auswirkungen dieser schon ausgeführten Befehle wieder rückgängig gemacht werden (Undo, Rollback). Daher erfolgt das Zurückschreiben nicht mehr direkt wie oben, sondern in einen internen Speicher, damit sie von nachfolgenden spekulativ ausgeführten Befehlen verwendet werden können. Erst wenn klar ist, dass diese Befehlskette auch wirklich ausgeführt werden soll, werden diese internen Zustände an die richtigen Stellen geschrieben; im anderen Fall wird dieser interne Zustand einfach weggeworfen. Diese Schlussphase wird als Pensionierung («retiring») der Instruktion bezeichnet.

Schauen wir uns das Beispiel in der Grafik an: Der erste Befehl wird bearbeitet, muss aber beim Laden eines Wertes auf den langsamen Hauptspeicher warten. Der nächste Befehl ist ein Sprungbefehl, der vom Resultat der vorherigen Instruktion abhängt. Da dieses noch nicht bereit ist, gibt es eine Sprungvorhersage und die nachfolgenden Befehle werden spekulativ ausgeführt. Erst, wenn klar ist, ob diese Vorhersage richtig war, wird entschieden, ob das interne Resultat weggeworfen oder offiziell wird.

2. Risiken und Nebenwirkungen

Angriffe

Die Angriffe nutzen nun aus, dass nicht der ganze Zustand wiederhergestellt wird, sondern der Cache auch weiterhin die Werte enthält, welche durch die spekulativ ausgeführten Instruktionen geladen wurden. Sie nutzen diese auf drei unterschiedliche Weisen.

Meltdown: Rechteanmassung

Ein Programm darf nicht auf den gesamten Speicher zugreifen, sondern nur auf Bereiche, die ihm auch zugewiesen wurden. Intel macht in seinen Prozessoren diese Überprüfung zu spät. Sie findet nämlich nicht dann statt, wenn der fragliche Operand geladen werden soll, sondern erst wenn der Befehl in Pension gehen soll.

Dadurch kann ein Programmierer in spekulativen Instruktionen auf Speicherbereiche zugreifen, die er sonst gar nicht zu sehen bekäme. Er kann das Resultat aber nicht verwenden, denn die Resultate des Befehls werden weggeworfen. Er kann aber aufgrund des gelesenen Wertes in weiteren spekulativen Befehlen den Cache so verändern, dass später im Programm dann Rückschlüsse auf diese gelesenen Daten möglich sind.

Damit kann Speicher ausgelesen werden, auf den das Programm eigentlich gar nicht zugreifen dürfte. Da der Lesebefehl aber ja nicht wirklich (sondern nur spekulativ) ausgeführt wird, gibt es auch kein Problem.

Damit lassen sich auf Intel-Prozessoren Speicherbereiche des Betriebssystems oder von anderen virtuellen Maschinen auslesen – eine Gefahr für alle Cloud-Dienste.

Spectre 1: Indexgrenzenüberschreitung

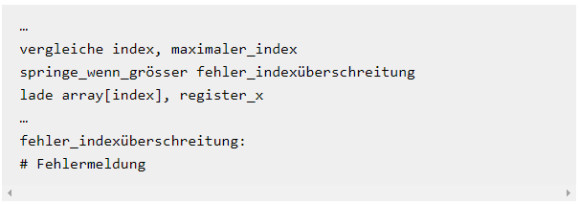

Programme greifen regelmässig auf Felder (Arrays) zu: Sequenzen von Speicheradressen, die zusammengehörige Informationen enthalten und durch eine Startadresse und eine Länge definiert sind. Die einzelnen Positionen sind durchnummeriert (indexiert); nur Positionen bis zur maximalen Länge sind gültig.

Mittels zu grosser Indizes könnte auf Bereiche ausserhalb des Arrays zugegriffen werden, Bereiche, an denen sich andere Daten befinden. Deshalb finden – insbesondere in Programmen, die mit Indizes arbeiten, die von aussen beeinflusst werden können – Überprüfungen statt, ob der Index auch innerhalb des gültigen Bereichs liegt:

Mittels zu grosser Indizes könnte auf Bereiche ausserhalb des Arrays zugegriffen werden, Bereiche, an denen sich andere Daten befinden. Deshalb finden – insbesondere in Programmen, die mit Indizes arbeiten, die von aussen beeinflusst werden können – Überprüfungen statt, ob der Index auch innerhalb des gültigen Bereichs liegt:

Der Spectre-1-Angriff greift nun genau hier ein: Da im Normalfall der Index im gültigen Bereich liegt, prognostiziert der Prozessor, dass der lade-Befehl ausgeführt werden soll und liest spekulativ aus dem ungültigen Bereich. Obwohl der Fehler später bemerkt wird und der gelesene Wert nie in einem normal zugreifbaren Register landet: Der Cache bleibt verändert und lässt durch sein Verhalten Rückschlüsse wie oben zu.

Spectre 2: Unterjubeln von Befehlen

In vielen Programmen werden sogenannte Sprungtabellen verwendet: Die Adresse des nächsten auszuführenden Befehls steht an einer spezifischen oder zu berechnenden Speicheradresse. Betriebssysteme und objektorientierte Programmiersprachen sind zwei fleissige Nutzer dieser Technik.

Beim Spectre-2-Angriff wird der Prozessor so vorbereitet, dass die Sprungvorhersage auf einen präparierten Codeblock zeigt. Auch hier werden die Befehle nur spekulativ ausgeführt, ihre Auswirkungen auf den Cache sind aber erkennbar.

Kernproblem

Das Kernproblem liegt darin, dass wir aus Effizienzgründen an vielen Stellen gemeinsame Ressourcen nutzen. Nicht nur im Prozessor, z.B. der Cache, sondern auch im Internet (gemeinsame Funkkanäle oder Leitungen), aber auch in der realen Welt (z.B. Schiene oder Strasse). Wenn mehrere Teilnehmer eine gemeinsame Ressource nutzen, können sie darüber miteinander kommunizieren, beispielsweise, indem der eine Teilnehmer die Auslastung dieser Ressource verändert und das Gegenüber diese Auslastung beobachtet. Damit wird diese Ressource zum Kommunikationskanal: einer von unzähligen verdeckten Kanälen oder Seitenkanälen.

Um diese Seitenkanäle zu nutzen, müssen beide Kommunikationspartner aktiv werden. Im Normalfall bedingt dies die freiwillige Teilnahme beider Seiten. In diesem Fall kann aber durch spekulative Ausführung (mit interner Umordnung der Befehle, «out-of-order execution») eine der beiden Kommunikationsseiten zur Zusammenarbeit übertölpelt werden. Damit wird die Spekulation nicht vollständig frei von Nebenwirkungen und damit entsteht die Möglichkeit eines Seitenkanals.

Das Problem besteht nur, solange gemeinsame Ressourcen und spekulative Ausführung zusammen auftreten. Beide sind aber Schlüsselstellen für die Effizienz der heutigen Prozessoren. Durch bessere Trennung des Caches für normale und spekulative Instruktionen (wie es schon heute für Schreibbefehle verwendet wird) könnte das erreicht werden. Durch die langen und teuren Entwicklungszyklen für Prozessoren werden wir erst in vielen Monaten mit Prozessoren rechnen dürfen, die das Problem nicht mehr haben.

Betroffen

- … von Meltdown sind laut aktuellem Informationsstand die meisten Intel-Prozessoren der letzten ca. 20 Jahre und einige neuere ARM-Prozessoren. Prozessoren anderer Hersteller, auch wenn sie x86-kompatibel sind, scheinen bisher nicht davon betroffen zu sein.

- … von Spectre 1 und 2 sind die meisten aktuellen Prozessoren, die spekulative Ausführung mit out-of-order execution verwenden, wenn auch in unterschiedlichem Ausmass. Insbesondere scheinen die meisten ARM-Prozessoren davon nicht betroffen zu sein. Insbesondere Spectre 1 scheint aber hauptsächlich Programme zu betreffen, die fremden Code ausführen. Prominente Beispiele sind da Webbrowser, die aber auch schon Gegenmassnahmen ergriffen haben.

Gegenmassnahmen

Alle drei Fälle basieren auf Fehlern der CPU; da Updates bei den CPUs jedoch schwierig sind und nur teilweise abhelfen, sind Betriebssysteme, Compiler und Anwendungsprogrammierer gefordert.

- Meltdown wird in vielen Betriebssystemen durch Änderung der Speicherorganisation verhindert. Bei jedem Betriebssystemaufruf sind neu teure Änderungen der Übersetzungstabelle notwendig. Dies führt jedoch zu Verlangsamungen, je nach Situation zwischen rund 5 % und 30 %, sehr selten bis fast 50 %.

- Spectre 1 (Arraygrenzen) wird zuallererst die Programmierer beschäftigen. Sie müssen sicherstellen, dass – wenn sie nicht vertrauenswürdigen Code in ihrer Anwendung ausführen – dieser dann (a) den Seiteneffekt nicht auslösen kann oder (b) ihn nicht messen kann. Vermutlich werden in den nächsten Monaten findige Entwickler von Compilern Optionen schaffen, um diese Situation automatisch zu erkennen und zu verhindern.

Da die Lücke aber nur Anwendungen betrifft, die fremden Code ausführen (JIT, Bytecode und eventuell auch Interpreter), aber alle Anwendungen verlangsamen, werden die betroffenen Anwendungsentwickler diese Funktion des Compilers wahrscheinlich zuerst aktivieren müssen. - Spectre 2 (Berechnete Sprünge) wird aktuell über Microcode- in Kombination mit Betriebssystem-Updates behoben. Alternativ kann auch sogenannter «RetPoline»-Code anstelle des berechneten Sprungs genutzt werden. Einige Compiler bieten bereits eine entsprechende Option an, Weitere werden folgen.

Bis die Sache ausgestanden ist, werden auch die Nutzer stark gefordert: Das fleissige und zeitnahe Einspielen von Anwendungs-, Betriebssystem- und BIOS/UEFI-Updates [3] sowie das Ausbaden unerwünschter Nebenwirkungen derselben werden dafür sorgen, dass uns allen noch über Monate hinweg nicht langweilig wird.

Fussnoten:

[1] Alternativ könnte er auch mit einer Wärmebildkamera die zuletzt angefassten Figuren identifizieren oder, oder, oder …

[2] Es gab einen Trend zu Prozessoren mit einfacheren Befehlen, die dann entsprechend schneller ausgeführt werden können (RISC-Prozessoren, insbesondere die in Mobilgeräten beliebten ARM-Prozessoren). Aber die klassischen CISC-Prozessoren mit ihrer grösseren Verbreitung und Marktmacht haben da einfach aufgeholt, indem sie intern wie RISC zu arbeiten begannen.

[3] Leider sind BIOS-/UEFI-Updates häufig nicht so einfach einzuspielen wie der Rest. Hier sind die Gerätehersteller gefordert.

Weiterführende Informationen

Deutsch:

- FAQ zu Meltdown und Spectre (Heise), inklusive vieler Links

- Benchmarks (Heise)

- Deutsche Erklärung (Proact)

Englisch:

- Webseiten zu den Spectre- und Meltdown-Attacken inklusive technischer/wissenschaftlicher Literatur (derzeit sind die beiden Webseiten bis auf das Favicon identisch)

- Erste Hinweise auf ein Sicherheitsproblem (LWN)

- Performanceanalysen von Phoronix und Andreas Freund (Postgres)

- Erster Überblick über die Sicherheitslücke sowie Hintergründe und Entstehungsgeschichte (The Register)

- Englische Erläuterung, inklusive Begründung, wieso der Raspberry Pi nicht betroffen ist

- Beschreibung der Sicherheitslücken für Programmierer (Google Project Zero)

- Test-Software, ob ein Linux-Rechner verwundbar ist

- Erläuterung zu RetPoline (Google)

- Caching war schon ein Problem in der Xbox 360

- Analyse von Prof. Steven Bellowin